Ge半導体と相性のよい電極材料としてBi₂Te₃を見つけ最適な接合方法を開発

- Siに次ぐ次世代半導体Geの本格的な実用化に期待 -

2025/07/31

発表のポイント

- シリコン(Si)の限界を超える次世代の半導体材料として期待されるゲルマニウム(Ge)ですが、電子が電気を運ぶn型Geでは電極との接触抵抗が大きく、実用化の大きな障壁となっていました。

- 研究チームは、電極材料としてテルル化ビスマス(Bi2Te3)を見出し、n型Geと接合し反応させることで、原子レベルで滑らかな界面を形成し、電子の流れを妨げる“エネルギー障壁(注1)”を、従来の最小値の約半分に当たる世界最小の0.26 eVにまで低減することに成功しました。

- Siよりも高性能な半導体として注目されるGeでこの課題を克服した本成果は、Geを用いた次世代CMOSデバイス(注2)の実現に向けた大きな一歩です。

概要

現在のスマートフォンやパソコンの性能を支えているのは、シリコン(Si)を使った半導体デバイスです。しかし、その性能をこれ以上高めることが難しくなってきています。そこで、次の主役として期待されているのが元素周期表でSiと同じ14族のゲルマニウム(Ge)です。ただし、Geを用いた半導体では、金属電極とn型Geとの界面に生じる高い接触抵抗が性能向上の妨げとなっており、実用化の大きな課題でした。

産業技術総合研究所先端半導体研究センターの張文馨(チャン・ウェンシン)主任研究員と東北大学グリーン未来創造機構グリーンクロステック研究センターの齊藤雄太教授(大学院工学研究科兼務)らは、層状物質であるテルル化ビスマス(Bi2Te3)薄膜とn型Geを反応させることで、非常に電気が流れやすい界面の形成に成功しました。今回実現した金属/半導体接合では、電子の流れを妨げる“エネルギー障壁”を世界最小の値にまで低減し、理想的な接合(オーミックコンタクト(注3))が実現されました。本研究は、次世代の高性能半導体デバイスの実現を加速させる成果として期待されます。

本成果は、2025年7月11日付(米国東部時間)に応用物理に関する材料分野の専門誌APL Materialsのオンライン版で公開されました。

研究の背景

これまで、シリコン(Si)を使った半導体チップが、スマートフォンやコンピュータなどの情報機器を支えてきました。しかし、今後主流になると見込まれる「2ナノメートル世代(注4)」以降では、チップをこれ以上微細化することで性能を向上させることが物理的に難しくなると考えられています。このため、Siに代わる新たな半導体材料の研究が世界中で進められています。

なかでもゲルマニウム(Ge)は、従来のSi製造プロセスとの高い互換性を持つことから、他の材料に比べて早期の実用化が期待されています。半導体には、主に「n型」と「p型」の2種類があり、n型は電子が、p型は正孔(ホール)と呼ばれる電子の抜け穴のようなものが電流を運ぶキャリアの役割を担います。論理回路などの半導体デバイスには、n型とp型を組み合わせて使う必要があります。Geはこれらキャリアの移動がSiよりも高速であることが知られています。

しかし、Geをn型で用いる場合、金属電極との接合部分で高い接触抵抗が生じ、十分な電流が流れないという課題がありました。これは、接合部分に“エネルギー障壁”が生じ、電子の通り道が妨げられることが原因です。この問題が、Geを用いた高性能半導体デバイスの実現を阻む大きな障壁となっていました。

今回の取り組み

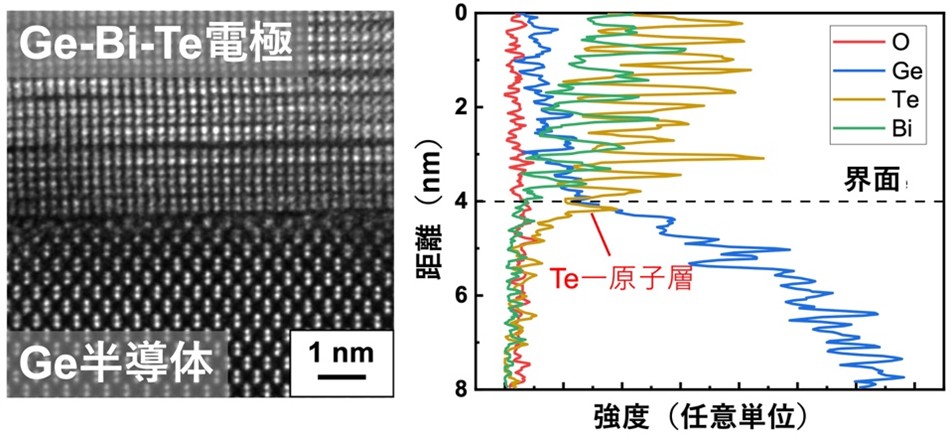

研究チームは、テルル化ビスマス(Bi2Te3)という材料をGeの上に薄く成膜し、400℃で加熱することで、両者の界面にファンデルワールス力に基づく非常にきれいで滑らかな界面を作ることに成功しました。さらに、この過程でBi2Te3とGeが反応し、Geの最表面にテルル(Te)の一原子層が並ぶ構造が現れ、異なる物質同士を結びつける疑似ファンデルワールス結合が形成され、原子レベルで高品質な界面が実現されました。

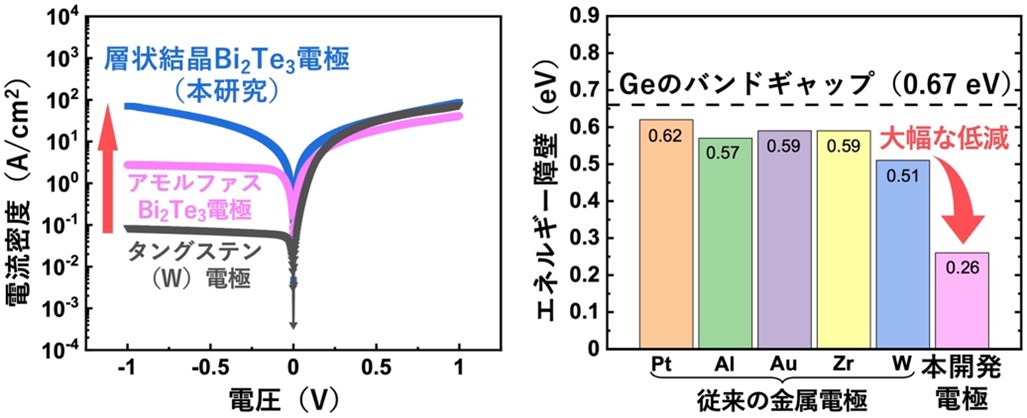

この界面では、Geの最表面に1層のTe原子が並び、Geとビスマス(Bi)、Teが順に重なるような構造が形成されました。このような構造では、界面部分に欠陥やダメージがほとんどなく、電気がスムーズに流れることが期待されました。実際に電気的特性を測定したところ、金属/半導体界面に存在する電子が通過するために必要なエネルギー(エネルギー障壁)が、これまでで最も小さかった0.51eVの約半分に当たる0.26 eVにまで低減し、Bi₂Te₃とn型Geの接続が理想的なオーミックコンタクトを示すことが明らかになりました。

これまでの技術では、電気の流れをよくするために極薄絶縁膜を接続部に挿入するなどの工夫が必要でしたが、今回の方法ではそのような追加構造を用いずに、接触抵抗を大幅に低減できた点が大きな成果です。また、n-Geとの接合の研究の多くはGe表面の結晶方位が(111)面の基板を用いたものでしたが、本研究は(100)基板において良好な電気特性を実現できました。

今後の展開

本研究では、Ge(100)という実用的な基板面において、Bi2Te3との間に非常に良好な接続を形成し、電気が流れやすい構造を実現できることを示しました。今後は、この技術を用いてトランジスタ(注5)を実際に作製し、その性能向上を検証していく予定です。

さらに、電子を流すn型Geだけでなく、正孔(ホール)を流すp型Geと組み合わせた「Ge CMOS回路」の開発につなげることで、現在のSi半導体を超える新しい世代の高性能チップの実現を目指していきます。

図1. (左)Ge-Bi-Te電極とGe半導体の断面の透過電子顕微鏡画像。原子レベルで平坦な擬似ファンデルワールス界面が観察できる。また、Ge-Bi-Teには原子が存在しない黒い線が観察されるが、これはファンデルワールスギャップであり、層状構造になっていることがわかる。(右)左図の上下方向の元素分析結果。Ge基板の最表面に、Teの一原子層が存在する。

図2. (左)様々な電極を用いた時の電流密度と印加した電圧の関係。従来のタングステン(W)電極は、正と負の電圧をかけた時のグラフの形が非対称で、電極とGe半導体界面に存在するエネルギー障壁の存在を示唆している。アモルファスのBi2Te3でも依然として非対称であったが、層状結晶のBi2Te3とすることで、対称的なオーミックコンタクトが実現できた。(右)本研究で得られた、世界最小のエネルギー障壁と他の文献との比較。

謝辞

本研究は、日本学術振興会(JSPS)科研費(JP23H01474)の支援を受けて行われました。

用語説明

(注1)エネルギー障壁

金属とn型半導体を接触させた時、n型半導体から金属に電子が流れるようにするために必要な最小のエネルギー。ショットキー障壁とも言います。

(注2)次世代CMOSデバイス

CMOS(相補型金属酸化膜半導体)デバイスは、電力効率と集積度に優れた論理回路の構成方式で、現在のスマートフォンやコンピュータなどに幅広く使われています。次世代CMOSデバイスは、これまでのシリコンに代わる新材料を導入し、さらなる性能向上を目指す新しい半導体技術を指します。

(注3)オーミックコンタクト

電極と半導体との接合部分において、電圧をかけたときに電流が線形に流れる、いわゆるオームの法則に従う接触のこと。電流の流れを妨げるエネルギー障壁が小さいため、スイッチング素子や回路が効率よく動作するために重要な要素です。

(注4)2ナノメートル世代

半導体チップの配線やトランジスタのサイズを示す指標で、1ナノメートルは10億分の1メートル。「2ナノメートル世代」とは、実際に最小寸法が2ナノメートルになっているわけではなく、積層した多層の半導体を従来の平面型のトランジスタ構造を想定した場合に、ゲート長が2ナノメートル相当の性能を有しているプロセス技術を指します。微細化とトランジスタ構造の発展が進むことで、より多くの回路を小さなチップに集積でき、処理性能の向上や省電力化が期待されます。

(注5)トランジスタ

電気信号を増幅したり、スイッチのように電流の流れを制御したりする半導体素子で、コンピュータやスマートフォンをはじめとするあらゆる電子機器の基本構成要素です。半導体チップには数十億個ものトランジスタが集積され、演算処理や記憶などを担っています。

論文情報

著者: Wen Hsin Chang*, Shogo Hatayama, Naoya Okada, Toshifumi Irisawa, and Yuta Saito*

*責任著者:産業技術総合研究所先端半導体研究センター 主任研究員 張文馨

DOI:doi.org/10.1063/5.0278628

URL:https://pubs.aip.org/aip/apm/article/13/7/071117/3352347/Realization-of-ideal-Ohmic-contact-to-n-Ge-The-key

お問合せ先

東北大学グリーンクロステック研究センター(大学院工学研究科 知能デバイス材料学専攻 兼務) 教授 齊藤 雄太

TEL:022-795-7360

E-mail:yuta.saito.e5@tohoku.ac.jp