量子ドットの電荷状態を高速に検出する解析手法を開発

- 量子コンピュータの読み出し速度向上や物性探索に期待 -

2025/04/09

発表のポイント

概要

量子コンピュータの基本素子である量子ビットの状態を高速・高精度に読み出すことは、量子情報処理において重要な課題です。特に半導体量子ドットでは、単一電子の電荷状態を検出する技術が量子ビット読み出しの鍵となっています。

東北大学材料科学高等研究所(WPI-AIMR)の篠﨑基矢特任助教と大塚朋廣准教授(電気通信研究所兼務)らの研究グループは、ベイズの定理に基づく逐次的な電荷状態推定手法を開発し、その性能を従来手法の閾値(しきいち)判定と比較しました。本研究では、測定信号のノイズ特性が電荷状態によって異なる条件下で、ベイズ手法が優れた性能を発揮することを確認しました。この方法により、リアルタイムでの電荷状態推定において、より多くの信頼性の高いデータ点を得ることができます。また、状態遷移近傍でも高精度な推定が可能であることも確認しました。本成果により、量子ビットやセンサなどの読み出しの高速化が期待され、将来の量子情報処理等への応用が期待されます。

本研究成果は、2025年3月26日(現地時間)に米国物理学会誌Physical Review Applied(電子版)に掲載されました。

研究の背景

半導体量子ドットを用いた量子ビットは、量子コンピュータの有力な実装方式の一つです。この量子ビットの状態読み出しでは、高感度な電荷センサ(注4)で検出する方法が広く使われています。しかし、センサの信号にはノイズが含まれており、正確な状態判定のためには何らかの信号処理が必要です。

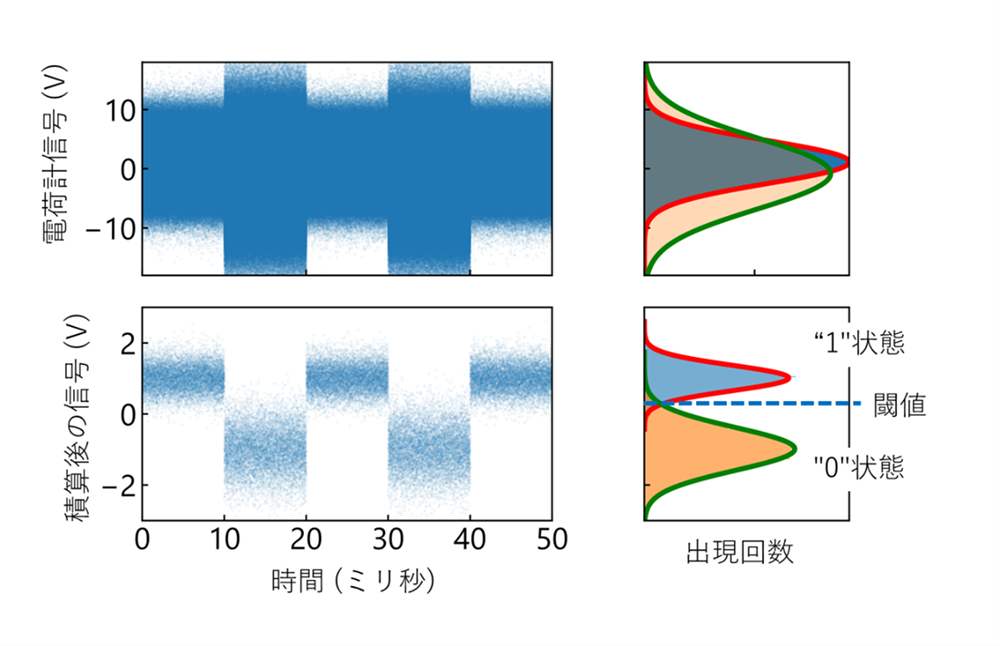

従来は信号を一定時間積算してノイズを低減し、その値が閾値を超えるかどうかで判定する「閾値判定法」が主流でした(図1)。この方法は単純ですが、十分な精度を得るため(信号対雑音比を向上させるため)の積算時間が実質的に読み出し速度を制限し、量子コンピュータの性能向上の課題となっていました。そのため、低ノイズアンプの開発など、ハードウェア面からの改善が進められてきましたが、本研究ではデータ解析アルゴリズムの観点からこの問題にアプローチしました。

今回の取り組み

研究グループは、ベイズの定理を活用した逐次的な電荷状態推定手法を開発しました。測定データから0か1かの状態を推定する過程は、まさにベイズの手法が得意とする問題です。開発した手法では、測定データが得られるたびにそれぞれの状態の推定確率を更新し、確率が要求値より高くなった時点で判定を確定します。これにより、必要最小限のデータで判定が可能になります。

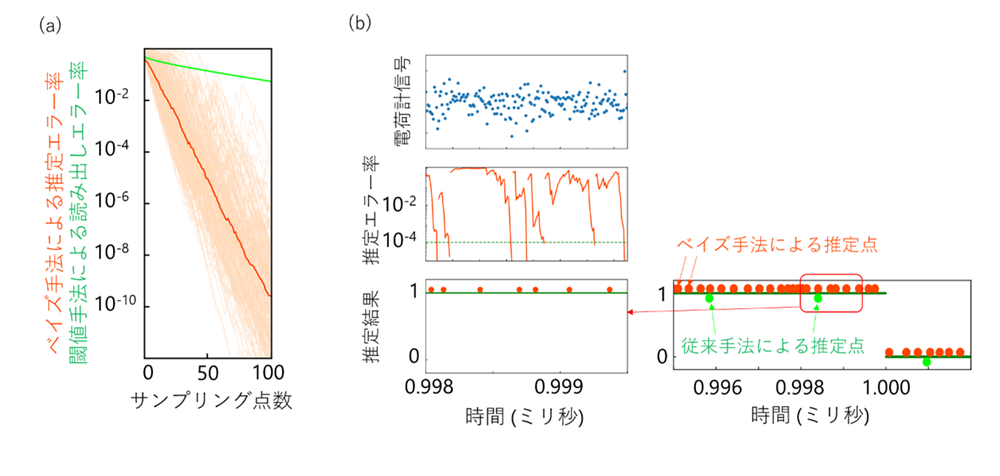

シミュレーションを用いて本手法による推定エラー率と従来手法によるエラー率を計算したところ、特に高感度な電荷センサで予想されるそれぞれの状態でノイズが異なる場合に、図2(a)のようにベイズ手法の優位性が顕著に現れました。例えば、ノイズの大きさの比が0.6の場合、従来手法と比べて約10分の1のデータ点で同等の精度を達成できることが示されました。これは読み出しの速度が10倍速くなることを意味します。

さらに図2(b)に示すように、研究グループは量子ドットの状態が変化する遷移領域においても、提案手法が従来手法より高い性能を示すことを確認しました。これによりリアルタイムな状態変化を検出する際にも本手法が有効であることがわかりました。

今後の展開

従来の閾値判定法はヒストグラム情報に立脚しており、測定値の時間的な変化という貴重な情報が失われていました。本研究で開発したベイズ手法は測定値の実時間情報を積極的に活用します。これは量子ドットだけでなく、ノイズ特性が複雑な他の計測系にも応用できる可能性があります。また、この手法は書き換え可能な集積回路のFPGA(注5)との親和性が高く、リアルタイム処理の実現に適しています。

このアプローチにより、量子ビット読み出しの高速化だけでなく、量子ドット電荷センサを活用した物性探索など、幅広い分野での応用が期待されます。

参考図

謝辞

本研究の一部は、JSPS科学研究費(JP21K18592, JP23H01789, JP23H04490, JP23KJ0200)、JSTさきがけ(JPMJPR16N3)、卓越研究員事業、東北大学人工知能エレクトロニクス卓越大学院プログラム等の支援を得て行われました。

用語説明

(注1)量子ドット

半導体などにおいて電子を閉じ込める微小な構造。サイズが小さいため、量子力学的な効果が現れ、電子のエネルギー状態が離散的になる。

(注2)ベイズの定理

ある条件の下での事象の確率(条件付き確率)を計算する方法。数式では P(A|B) = P(B|A)×P(A)/P(B) と表される。本研究では、測定値(結果)から電荷状態(仮説)の確率を逐次的に更新する際にこの定理を用いた。

(注3)量子ビット

量子状態を利用して演算を行うための素子。量子コンピュータの基本構成素子となる。

(注4)電荷センサ

電子1個の電荷を検出できる高感度なセンサ。近くの電子の有無によって電気抵抗が変化する性質を利用している。

(注5)FPGA (Field-Programmable Gate Array)

製造後にプログラムによって内部の回路構成を変更できる集積回路。高速なデータ処理が可能であり、リアルタイム制御などに適している。

論文情報

著者: Motoya Shinozaki*, Yui Muto, Takahito Kitada, and Tomohiro Otsuka*

*責任著者: 東北大学材料科学高等研究所 特任助教 篠﨑基矢

東北大学材料科学高等研究所 准教授 大塚朋廣

掲載誌: Physical Review Applied

DOI: 10.1103/PhysRevApplied.23.034078

お問合せ先

東北大学材料科学高等研究所 (WPI-AIMR)

(兼)東北大学 電気通信研究所

(兼)東北大学 大学院工学研究科

(兼)東北大学 Tohoku Quantum Alliance (TQA)

(兼)東北大学 先端スピントロニクス研究開発センター

准教授 大塚 朋廣

TEL:022-217-5509

E-mail:tomohiro.otsuka@tohoku.ac.jp